Early adopters are already using the Pegasus Verification System for large-scale designs, across storage, high-performance computing, cloud, server and mobile applications. The solution offers customers the following benefits:

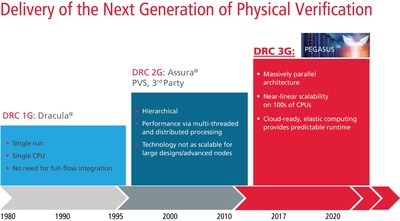

- Massively parallel architecture: The solution incorporates a massively parallel architecture that provides unprecedented speed and capacity, enabling designers to easily run on hundreds of CPUs to speed up tapeout times.

- Reduced full-chip physical verification runtimes: The solution's gigascale processing offers near-linear scalability that has been demonstrated on up to 960 CPUs, allowing customers to dramatically reduce DRC signoff runtimes.

- Low transition cost: Using existing foundry-certified rule decks, customers achieve 100 percent accurate results with a minimal learning curve.

- Flexible cloud-ready platform: The solution offers native cloud support that provides an elastic and flexible compute environment for customers facing aggressive time-to-market deadlines.

- Efficient use of CPU resources: The solution's data flow architecture enables customers to optimize CPU usage, regardless of machine configurations and physical location, providing maximum flexibility to run on a wide range of hardware, achieving the fastest DRC signoff.

- Native compatibility with Cadence digital and custom design flows: The Pegasus Verification System integrates seamlessly with the Virtuoso® custom design platform, delivering instantaneous DRC signoff checks to guide designers to a correct-by-construction flow that improves layout productivity. An integration with the Innovus™ Implementation System enables customers to run the Pegasus Verification System during multiple stages of the flow for a wide range of checks—signoff DRC and multi-patterning decomposition, color-balancing to improve yield, timing-aware metal fill to reduce timing closure iterations, incremental DRC and metal fill during engineering change orders (ECOs) that improve turnaround time, and full-chip DRC.

Texas Instruments (TI), an early Cadence Pegasus Verification System customer, was able to successfully scale the new solution with significant improvements. The Pegasus Verification System's native cloud processing capabilities delivered improved turnaround times when compared with TI's incumbent solution.

Additionally, Scott Barrick, senior manager of advanced engineering services at Microsemi Corporation (NASDAQ: MSCC) said, "As technology nodes advance, Microsemi is leveraging the Cadence Pegasus Verification System to shorten our time to tapeout. Its near-linear scalability can enable us to scale full-chip DRC runs to hundreds of CPUs for short periods and achieve up to 10 times the speedup when compared with the previous-generation Cadence solution. The next-generation solution offers native cloud support and gigascale processing, giving us the flexibility to add hundreds of CPUs for peak usage during tapeout while achieving our desired runtime."

"Engineers have experienced increasing DRC complexity at advanced nodes, and current DRC solutions can't support the turnaround requirements needed to ensure that design schedules are met," said Dr. Anirudh Devgan, executive vice president and general manager of the Digital & Signoff Group and the System & Verification Group at Cadence. "The Pegasus Verification System's innovative architecture and native cloud-ready processing provides an elastic and flexible computing environment, which can enable our customers to complete full-chip signoff DRC on advanced-node designs in a matter of hours, speeding time to market."

The new Pegasus Verification System continues to extend the organic innovation within the Cadence digital design and signoff suite. The suite includes a comprehensive full flow from synthesis through implementation and signoff, offering the fastest path to achieve power, performance and area (PPA) targets across a wide variety of applications and vertical segments. The addition of the Pegasus Verification System to the full-flow suite also supports the company's broader System Design Enablement (SDE) strategy, which enables system and semiconductor companies to create complete, differentiated end products more efficiently.

About Cadence

Cadence enables electronic systems and semiconductor companies to create the innovative end products that are transforming the way people live, work and play. Cadence software, hardware and semiconductor IP are used by customers to deliver products to market faster. The company's System Design Enablement strategy helps customers develop differentiated products—from chips to boards to systems—in mobile, consumer, cloud datacenter, automotive, aerospace, IoT, industrial and other market segments. Cadence is listed as one of Fortune Magazine's 100 Best Companies to Work For. Learn more at

cadence.com.

© 2017 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo and the other Cadence marks found at www.cadence.com/go/trademarks are trademarks or registered trademarks of Cadence Design Systems, Inc. All other trademarks are the property of their respective owners.

For more information, please contact:

Cadence Newsroom

408-944-7039

newsroom@cadence.com

To view the original version on PR Newswire, visit: http://www.prnewswire.com/news-releases/cadence-launches-the-pegasus-verification-system-a-massively-parallel-physical-signoff-solution-300437704.html

SOURCE Cadence Design Systems, Inc.

| Contact: |

| Cadence Design Systems, Inc.

Microsemi Corporation Web: http://www.cadence.com |