Massively parallel architecture scales linearly beyond 10M instances while improving power, performance and area

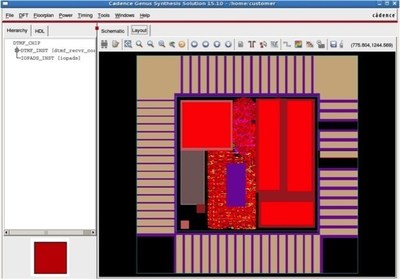

SAN JOSE, Calif., June 3, 2015 — (PRNewswire) — Cadence Design Systems, Inc. (NASDAQ: CDNS) today unveiled the Cadence® Genus™ Synthesis Solution, its next-generation register-transfer level (RTL) synthesis and physical synthesis engine, to address the productivity challenges faced by RTL designers. Genus Synthesis Solution incorporates a multi-level massively parallel architecture that delivers up to 5X faster synthesis turnaround times and scales linearly beyond 10M instances. In addition, the tool's new physically aware context-generation capability can reduce iterations between unit- and chip-level synthesis by 2X or more. This powerful combination enables up to 10X improvement in RTL design productivity.For more information on Genus Synthesis Solution, please visit www.cadence.com/news/genus.

Key Genus Synthesis Solution features and capabilities include:

- Massively parallel architecture – The tool performs timing-driven distributed synthesis of a design across multiple cores and machines. All key steps in the synthesis flow leverage both multiple machines and multiple CPU cores per machine.

- Physically aware context generation – The complete timing and physical context for any subset of a design can be extracted and used to drive RTL unit-level synthesis with full consideration of chip-level timing and placement, significantly reducing iterations between chip-level and unit-level synthesis runs.

- Unified global routing with Innovus™ Implementation System – Genus Synthesis Solution and Cadence Innovus Implementation System, a next-generation physical implementation solution, share an enhanced 4X faster timing-driven global router that enables tight correlation of both timing and wirelength to within 5 percent from synthesis to place and route.

- Global analytical architecture-level PPA optimization – The solution incorporates a new datapath optimization engine that concurrently considers many different datapath architectures across the whole design and then leverages an analytical solver to pick the architectures that achieve the globally optimal PPA. This engine delivers up to 20 percent reduction in datapath area without any impact on performance.

"Processors for automotive and industrial markets are driving higher-levels of integration and complexity. This requires larger design partitions to deliver the efficiencies and time-to-market demanded by our customers," said Anthony Hill, Director of Processor Technology, Texas Instruments (TI). "The highly-scalable Genus Synthesis Solution from Cadence has enabled more than a 5x improvement in turnaround time, enabling us to realize production-quality timing-driven synthesis of up to three-million instance partitions in less than eight hours."

"With Genus Synthesis Solution, we see a significant opportunity to improve RTL design productivity and make more aggressive architecture-level optimizations to improve PPA," said Dr. Anirudh Devgan, senior vice president and general manager of the Digital & Signoff Group at Cadence. "Early customers are already deploying the solution in their RTL design flows and reporting significantly better turnaround times and throughput compared to competing solutions."

About Cadence

Cadence enables global electronic design innovation and plays an essential role in the creation of today's integrated circuits and electronics. Customers use Cadence software, hardware, IP and services to design and verify advanced semiconductors, consumer electronics, networking and telecommunications equipment, and computer systems. The company is headquartered in San Jose, Calif., with sales offices, design centers and research facilities around the world to serve the global electronics industry. More information about the company, its products and its services is available at

www.cadence.com.

© 2015 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence and the Cadence logo are registered trademarks and Genus and Innovus are trademarks of Cadence Design Systems, Inc. in the United States and other countries. All rights reserved. All other trademarks are the property of their respective owners.

For more information, please contact:

Cadence Newsroom

408-944-7039

Email Contact

Video -

http://origin-qps.onstreammedia.com/origin/multivu_archive/PRNA/ENR/0-Cadence-Genus-Paul-Cunningham.mp4

Photo -

http://photos.prnewswire.com/prnh/20150603/220433

Logo -

http://photos.prnewswire.com/prnh/20140102/SF39436LOGO

To view the original version on PR Newswire, visit: http://www.prnewswire.com/news-releases/cadence-introduces-genus-synthesis-solution-delivering-up-to-10x-improvement-in-rtl-design-productivity-300093319.html

SOURCE Cadence Design Systems, Inc.

| Contact: |

| Cadence Design Systems, Inc.

Web: http://www.cadence.com |