Grenoble, France, July 17, 2024. Today, Defacto announced a new flow to generate automatically Arm-based System on Chips.

This year, Defacto and Arm developed a joint SoC design flow to help Arm users cover all needed automation—from SoC design architecture and exploration to top-level generation of all needed files for implementation and verification flows.

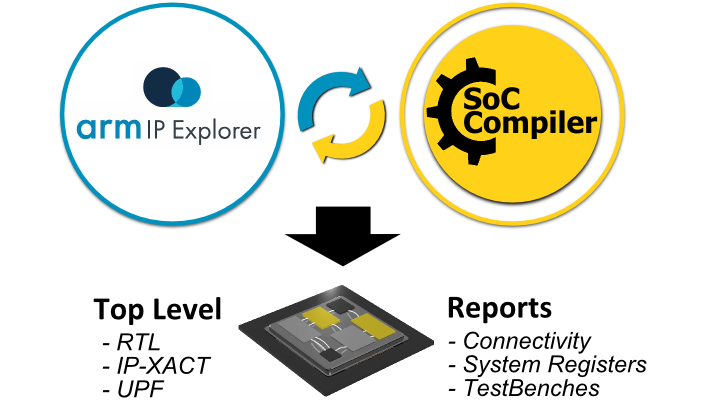

Through the intuitive graphical interface from the Arm design platform, Arm IP Explorer, helps make specification of the SoC easy and user friendly. Once SoC exploration is realized, RTL and IP-XACT design files are automatically generated using Defacto’s SoC Compiler design solution.

The jointly developed solution is built around a strong link between Arm IP Explorer and Defacto’s SoC Compiler to enable users to generate quickly several SoC design configurations. The speed of the Defacto SoC Compiler enables the generation of a multitude of SoC configurations based on different user specifications. With this solution, the overall design time from specification to an SoC ready for synthesis can be significantly reduced.

How it works? The joint Arm IP Explorer/SoC Compiler solution is the shortest path from the definition of Arm-based system architecture to implementation and design verification.

The first step is that users access Arm IP Explorer and start selecting IP cores from the catalog. IP parameters can be set at this level. With the selected IPs, users can architect the complete system. The platform gives also the flexibility to add custom IPs to reflect the desired system.

Integration checks are performed on-the-fly, and the completed and validated system can be exported to the Defacto SoC Compiler, which automatically generates the top-level IP-XACT / RTL / UPF files, along with different reports about connectivity density, chip size, and power consumption. The generated files are fully compatible with standard RTL2GDS SoC design flows. With the simplicity, speed, and flexibility of this solution, users can quickly and automatically explore and generate several SoC design configurations.

More information can be found on the Defacto page on the Arm partner website: https://www.arm.com/partners/catalog/defacto-technologies

To have a dedicated demo and presentation of the flow, feel free to Email Contact

About Defacto:

Defacto Technologies is an innovative chip design software company providing breakthrough RTL platforms to enhance integration, verification and Signoff of IP cores and System on Chips.

By adopting Defacto’s SoC Compiler design solutions, major semiconductor companies are continuously moving from traditional and painful SoC design tasks to a fully automated design methodology. The related ROI has been proven for hundreds of projects.

Defacto’s SoC Compiler enables designers of large Arm-based SoCs to find all the automation that is needed to insert Arm IP cores, connect them, restructure the overall design based on physical, power, or other criteria, and finally, generate all needed files for synthesis and verification processes.