Validation chip in fab will prove out the IP for integration in MCUs, SoCs and other semiconductor logic devices

MOUNTAIN VIEW, Calif., Aug. 29, 2016 — (PRNewswire) — Flex Logix Technologies, Inc., the leading developer of reconfigurable RTL IP cores and software, today announced it has completed design of a family of reconfigurable IP cores for TSMC 40ULP. Now in fabrication and expected to be fully validated in silicon during Q4 2016, the EFLX IP Core family for TSMC 40ULP will enable customers to design their next-generation MCUs and SoCs with reconfigurable RTL that can be quickly, easily and cost-effectively updated or changed at any time after fabrication, even in-system. This flexibility will enable customers to lower design costs and significantly speed time to market by eliminating the need to redo masks every time a change is needed for changing standards and for customer requests.

"As every chip designer knows, having to change the RTL blocks at any point in the design process could easily cost multiple millions of dollars and add three-to-six months to the design schedule," said Geoff Tate, CEO and co-founder of Flex Logix. "By making our reconfigurable IP cores available on TSMC 40ULP processes, we can bring the benefits of our flexible platform to a much larger audience designing next generation silicon."

About the EFLX IP core family in TSMC 40ULP

Flex Logix' IP core family for TSMC 40ULP consists of 10 hard IP cores:

- EFLX-100 Logic IP core: 120 LUTs (each LUT is dual 4-input look-up-tables with dual flip flops) of reconfigurable logic with reconfigurable interconnect, clocks, configuration. logic/memory and 304 I/O in 0.13 mm2. Each is available in five different threshold voltage (VT) combinations to fit customers' designs and power/performance tradeoffs

- EFLX-100 DSP IP core: 88 LUTs and 2 MACs (22x22 multiplier with pre-adder and 48-bit post-adder), with the same I/O and area as the EFLX-100 Logic IP core. This is also available in five different VT combinations.

- The EFLX-100 IP cores can be arrayed to make larger arrays up to 5x5 with any combination of Logic and DSP IP cores inter-mixed. This means that there are 25 different possible array sizes/dimensions from 120 LUTs to 3000 LUTs; and hundreds of unique arrays possible considering combinations of Logic and DSP.

- The EFLX-100 IP cores/arrays in TSMC 40ULP require only 5 metal layers and support multiple clocks.

EFLX-100 performance for the most popular VT combination (SVT for the performance logic and eHVT for the configuration bits) is 271MHz for a 16-bit counter (TT, 85C, 1.1V); and deep sleep mode power for a single core is 0.4μW (TT, 85C, 0.9V). State is retained down to 0.5V to enable an even lower power option.

Validation Silicon in Fab

Flex Logix proves out all of its IP cores in silicon to ensure low risk of integration, even though its IP is all digital and compatible with logic DRC rules and the IP is simulated under worst case conditions: maximum frequency, >90% utilization and RTL with very high toggle rates to check for worst case static and dynamic IR drops. Validation verifies in silicon that the recommended power grid architecture enables full speed operation at full utilization with high toggle rates under worst case conditions. The company tests each VT combination and checks enough array combinations to be sure that the inter-core array-interconnect is functional on all sides thus ensuring array reliability.

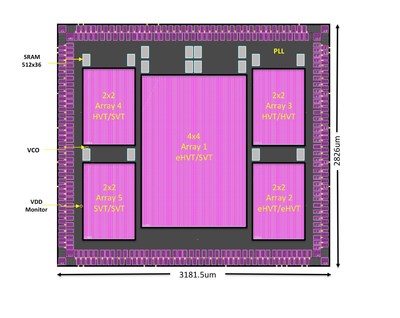

Below is the GDS-II of its TSMC 40ULP validation chip which is now in fabrication, and expected to complete validation in Q4/2016.

Photo: http://photos.prnewswire.com/prnh/20160828/401965

Flex Logix uses an on-chip PLL, from True Circuits, to test at frequencies of 300MHz and above to confirm all functional and performance operation over the full temperature and voltage range.

The validation chip is 9 square millimeters total.

Customers can choose the VT combination that gives them optimum combination of power and performance. Configuration bits and static logic can be one VT and dynamic logic another VT. There are 5 possible combinations. A 2x2 EFLX array is available for four of the VT combinations, with a large 4x4 EFLX array of the eHVT/SVT combination. Each array has a mix of DSP and Logic versions of the EFLX-100 core. Each EFLX array interconnects with external I/O for test and with 18 banks of on-chip SRAM (512x36) for high speed pattern testing. In total the validation chip has 32 EFLX-100 IP cores occupying about 4.2 square millimeters (0.13 square millimeters each).

Each array has a voltage monitor. There are 2 process monitor VCOs.

Power domains are dedicated to each EFLX array and separately for SRAM and I/O and PLL so voltage range can be measured precisely for each IP block and so state retention down to 0.5V can be confirmed.

Once validation is complete, a detailed validation report will be available under NDA to interested customers (just as we have now for TSMC 28HPM/C).

About True Circuits

True Circuits is a leading provider of timing IP and offers the industry's largest portfolio of low-jitter, silicon proven, general purpose and high performance PLLs and DLLs for a wide range of applications in all the major silicon foundry processes.

About Flex Logix

Flex Logix, founded in March 2014, provides solutions for reconfigurable RTL in chip and system designs using embedded FPGA IP cores and software. The company's technology platform delivers significant customer benefits by dramatically reducing design and manufacturing risks, accelerating technology roadmaps, and bringing greater flexibility to customers' hardware. Flex Logix recently secured $7.4 million of venture backed capital. It is headquartered in Mountain View, California and has sales rep offices in China, Europe, Israel, Taiwan and Texas. More information can be obtained at http://www.flex-logix.com or follow on Twitter at @efpga.

PRESS CONTACT:

Kelly Karr

Tanis Communications, Inc.

Email Contact

+408-718-9350

Logo - http://photos.prnewswire.com/prnh/20160731/394413LOGO

To view the original version on PR Newswire, visit: http://www.prnewswire.com/news-releases/flex-logix-reconfigurable-low-power-ip-cores-now-available-for-tsmc-40ulp-300319109.html

SOURCE Flex Logix Technologies, Inc.

| Contact: |

| Flex Logix Technologies, Inc.

Web: http://www.flex-logix.com |