Synopsys' Process Explorer and Raphael accurately simulate parasitic resistance of alternative metals and liner-barrier materials at the 7nm node and beyond

MOUNTAIN VIEW, Calif., July 11, 2016 — (PRNewswire) — World-leading nano-electronics research center imec and Synopsys, Inc. (NASDAQ: SNPS) today announced an interconnect resistivity model to support the screening and selection of alternative interconnect metals and liner-barrier materials at the 7nm node and beyond. With the continued scaling of advanced process nodes, the impact of parasitic interconnect resistance on the switching delay of standard cells rises considerably. The new model developed through this collaboration enables the evaluation of interconnect material and process options through simulations in the early stages of technology development, when wafer data is not available, and in the process optimization and integration stages of technology development, where it reduces expensive and time-consuming wafer-based iterations."We have already released to our partners a number of sets of model parameters related to various liner/barrier systems for Cu metallization or to alternative metals, such as Ru and Co, which they will use to screen metallization options for next-generation interconnect technologies," stated Dan Mocuta, director, Logic Device and Integration at imec.

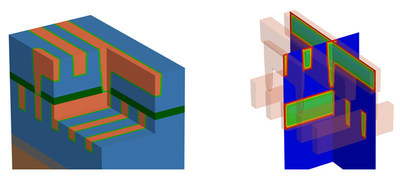

To use the new resistivity model, customers simulate the fabrication of the interconnect structure in 3D using the Synopsys process emulation tool Process Explorer, and then simulate the wire and via resistance in Raphael, the Synopsys gold standard interconnect field solver. This simulation flow accounts for the impact of layout rules, multi-patterning flows, and process-induced 3D features on the resistance of any conductive net in a multilayer interconnect stack, thereby predicting the influence of material, process and patterning choices on the interconnect resistance at scaled dimensions.

Imec has calibrated the resistivity model to wafer data for Cu, W, Ru and Co interconnects.

"The new resistivity model developed through this collaboration with imec is an important component of our pre-wafer simulation solution to enable our mutual customers to perform early screening of interconnect technology options at advanced nodes," said Dr. Howard Ko, senior vice president and general manager of the Silicon Engineering Group at Synopsys.

Imec's research into advanced logic scaling is performed in cooperation with imec's key partners in its core CMOS programs including GlobalFoundries, Intel, Micron, SK Hynix, Samsung, TSMC, Huawei, Qualcomm and Sony.

About imec

Imec performs world-leading research in nanoelectronics and photovoltaics. Imec leverages its scientific knowledge with the innovative power of its global partnerships in ICT, healthcare and energy. Imec delivers industry-relevant technology solutions. In a unique high-tech environment, its international top talent is committed to providing the building blocks for a better life in a sustainable society. Imec is headquartered in Leuven, Belgium, and has offices in Belgium, the Netherlands, Taiwan, USA, China, India and Japan. Its staff of about 2,500 people includes about 740 industrial residents and guest researchers. In 2015, imec's revenue (P&L) totaled 415 million euro. Further information on imec can be found at www.imec.be. Stay up to date about what's happening at imec with the monthly imec magazine, available for tablets and smartphones (as an app for iOS and Android), or via the website www.imec.be/imecmagazine.

Imec is a registered trademark for the activities of IMEC International (a legal entity set up under Belgian law as a "stichting van openbaar nut"), imec Belgium (IMEC vzw, supported by the Flemish Government), imec the Netherlands (Stichting IMEC Nederland, part of Holst Centre which is supported by the Dutch Government), imec Taiwan (IMEC Taiwan Co.), imec China (IMEC Microelectronics Shanghai Co. Ltd.), imec India (Imec IMEC India Private Limited) and imec USA (IMEC Inc).

About Synopsys

Synopsys, Inc. (Nasdaq: SNPS) is the Silicon to Software™ partner for innovative companies developing the electronic products and software applications we rely on every day. As the world's 15th largest software company, Synopsys has a long history of being a global leader in electronic design automation (EDA) and semiconductor IP and is also growing its leadership in software quality and security solutions. Whether you're a system-on-chip (SoC) designer creating advanced semiconductors, or a software developer writing applications that require the highest quality and security, Synopsys has the solutions needed to deliver innovative, high-quality, secure products. Learn more at www.synopsys.com.

Editorial Contact:

Tess Cahayag

Synopsys, Inc.

650-584-5446

Email Contact

Photo - http://photos.prnewswire.com/prnh/20160708/387633

To view the original version on PR Newswire, visit: http://www.prnewswire.com/news-releases/imec-and-synopsys-collaborate-on-interconnect-resistivity-model-to-enable-early-screening-of-interconnect-technology-options-at-advanced-nodes-300296208.html

SOURCE Synopsys, Inc.

| Contact: |

| Synopsys, Inc.

Web: http://www.synopsys.com |