Imperas leading commercial simulation technology combined with Metrics’ cloud-based verification platform is forming the basis for a new hardware design verification framework for RISC-V Cores

ZURICH — (BUSINESS WIRE) — June 10, 2019 — Imperas Software Ltd., the leader in virtual platforms and high-performance software simulation, today announced the collaboration with Metrics, working on the verification challenges required for RISC-V cores to achieve the required tape-out-ready quality for broad adoption by silicon designers. Imperas and Metrics will be demonstrating the early stages of this framework using the Google open source Instruction Stream Generator ( https://github.com/google/riscv-dv) for RISC-V processors and Google cloud services at the RISC-V Workshop Zurich this week.

This press release features multimedia. View the full release here: https://www.businesswire.com/news/home/20190610005655/en/

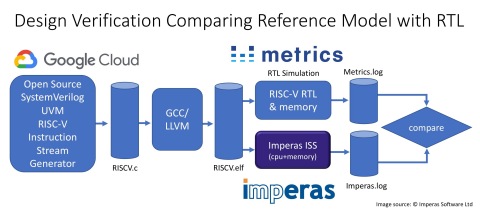

DV (Design Verification) framework for RISC-V Cores with Imperas commercial simulation technology combined with Metrics’ cloud-based verification platform (Graphic: Business Wire)

The Open ISA (Instruction Set Architecture) of RISC-V is enabling a new generation of devices based on an open flexible architecture that permits free adoption and implementation with custom instruction and extensions. In addition to the design freedoms, an open ISA also permits the development of ecosystems and IP supplier alternative options: which includes the traditional IP vendor business model, individual developments or collaborative open source projects.

The RISC-V Foundation’s Compliance Working Group is addressing the unique requirement to test and verify implementations are compliant to the specification. However, until now the more extensive functional design verification effort has not been addressed. This Imperas and Metrics collaboration makes industry best practices available to both commercial and open source RISC-V cores such as the CORE-V family from the OpenHW Group. With the OpenHW CORE-V family RISC-V core development teams will have access to curated and maintained high-quality repositories adopting industry leading standards for testing and verifying cores.

Using Google cloud services, the open source SystemVerilog UVM-based Instruction Stream Generator open sourced and maintained by Google and the framework that Metrics and Imperas are working on will help form the basis of an ‘off-the-shelf’ test and verification solution for RISC-V cores. Imperas reference simulator and envelope model covers the full range of the latest ratified RISC-V specification. Using an elastic database and Google cloud storage, the Metrics Platform manages big simulation data across regression environments. It offers access to on-demand simulation to meet peak usage and, unlike the traditional software license model, matches demand to job resources through a Software-as-a-Service (SaaS) business model, facilitating delivery and support.

“Open source hardware IP is the next stage of industry collaboration, combining with the flexibility of an open ISA such as RISC-V also highlights the need for high quality and robust verification efforts,” said Simon Davidmann, president and CEO of Imperas. “The commercial ecosystem that has supported many processor innovations over time, and continues to evolve in a symbiotic fashion, is collaborating on these foundational efforts to ensure high-quality hardware.”

“Verification for a design prior to tape-out (release for manufacture) is one of the most critical elements for the project schedule and the verification flow for an open source core is even more critical as until now this was not addressed by the business models of the traditional EDA tools community,” said Doug Letcher, CEO, Metrics. “The use of our SystemVerilog simulator in the Metrics Cloud Platform provides access to infinite simulation to meet these demanding verification needs.”

“The success of RISC-V will be measured not just in the adoption of the open ISA but in the ecosystem and collaboration that forms to address and support all aspects of SoC design flows and software development," says Calista Redmond, CEO of the RISC-V Foundation. “The open source hardware IP momentum is a tremendous force for change across the semiconductor industry, and quality and verification will be essential for the adoption of RISC-V open source cores.”

“Verification of a processor is a complex task and is a key factor when selecting IP cores,” said Rick O' Connor, President and CEO, OpenHW Group. “The OpenHW Group was created in part to develop an open source, collaborative, UVM based verification test bench to validate our CORE-V family of open source RISC-V core for use in high-volume production SoCs. The integration of Google’s instruction stream generator by Imperas and Metrics is an excellent way for the community to collaborate and build the OpenHW Group CORE-V test bench in a cloud-based infrastructure.”

About Imperas

Imperas is revolutionizing the development of embedded software and

systems and is the leading provider of RISC-V processor models and

virtual prototype solutions. Imperas, along with Open Virtual Platforms

(OVP), promotes open source model availability for a spectrum of

processors, IP vendors, CPU architectures, system IP and reference

platform models of processors and systems ranging from simple single

core bare metal platforms to full heterogeneous multi-core systems

booting SMP Linux. All models are available from Imperas at

www.imperas.com

and the

Open

Virtual Platforms (OVP) website.