- New Speedster7t family optimized for machine-learning and high-bandwidth networking applications

SANTA CLARA, Calif., May 21, 2019 — (PRNewswire) — Achronix Semiconductor Corporation, a leader in FPGA-based hardware accelerator devices and high-performance eFPGA IP, today introduced an innovative, new FPGA family, to meet the growing demands of artificial intelligence/ machine learning (AI/ML) and high-bandwidth data acceleration applications. The Achronix Speedster®7t family – based on a new, highly optimized architecture – goes beyond traditional FPGA solutions featuring ASIC-like performance, FPGA adaptability and enhanced functionality to streamline design.

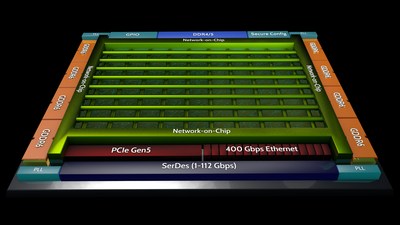

Specifically designed for AI/ML and high-bandwidth workloads, the Speedster7t FPGA family features a revolutionary new 2D network-on-chip (NoC), and a high-density array of new machine learning processors (MLP). Blending FPGA programmability with ASIC routing structures and compute engines, the Speedster7t family creates a new "FPGA+" class of technology.

As use cases for AI/ML are rapidly evolving, new solutions are required to address the varying requirements of high performance, flexibility and time to market. As a result, Semico Research Corp. forecasts the market size for FPGAs in AI applications will grow by 3x in the next four years to $5.2 billion.

"We are at the beginning of a high-growth phase of intelligent, self-learning computation that will have broad impacts on all aspects of our daily lives," said Robert Blake, President and CEO of Achronix Semiconductor. "The Speedster7t family is the most exciting announcement in the history of Achronix, representing innovation and learning across four architectural generations of hardware and software development and close cooperation with our lead customers. The Speedster7t family is the fusion of flexible FPGA technology with ASIC core efficiency to deliver a new "FPGA+" class of chips that truly push the boundaries of high-performance compute acceleration."

In developing the Speedster7t family of FPGAs, Achronix's engineering team redesigned the entire FPGA architecture to balance on-chip processing, interconnect and external I/O, to maximize the throughput of data-intensive workloads such as those found in edge- and server-based AI/ML applications, networking and storage.

Manufactured on TSMC's 7nm FinFET process, Speedster7t devices are designed to accept massive amounts of data from multiple high-speed sources, distribute that data to programmable on-chip algorithmic and processing units, and then deliver those results with the lowest possible latency. Speedster7t devices include high-bandwidth GDDR6 interfaces, 400G Ethernet ports, and PCI Express Gen5 — all interconnected to deliver ASIC-level bandwidth while retaining the full programmability of FPGAs.

"The new Achronix Speedster7t FPGA family is a prime example of the explosion of innovative silicon architectures created to handle massive amounts of data that are aimed directly at AI applications," said Rich Wawrzyniak, principal market analyst for ASIC & SoC at Semico Research. "Combining math functions, memory and programmability into their machine learning processor, combined with the cross-chip, two-dimensional NoC structure, is a brilliant method of eliminating bottlenecks and ensuring the free flow of data throughout the device. In AI/ML applications, memory bandwidth is everything and the Achronix Speedster7t family delivers impressive performance metrics in this area."

Optimized for Compute Performance

At the heart of Speedster7t FPGAs are a massively parallel array of programmable compute elements within the new MLPs that deliver the industry's highest FPGA-based compute density. The MLPs are highly configurable, compute-intensive blocks that support integer formats from 4 to 24 bits and efficient floating-point modes including direct support for TensorFlow's 16-bit format as well as the supercharged block floating-point format that doubles the compute engines per MLP.

The MLPs are tightly coupled with embedded memory blocks, eliminating the traditional delays associated with FPGA routing to ensure that data is delivered to the MLPs at the maximum performance of 750 MHz. This combination of high-density compute and high-performance data delivery results in a processor fabric that delivers the highest usable FPGA-based tera-operations per second (TOps).

World-class Bandwidth

Critical for high-performance compute and machine learning systems is high off-chip memory bandwidth to source and buffer multiple data streams. Speedster7t devices are the only FPGAs with support for GDDR6 memories, the highest bandwidth external memory devices. With each of the GDDR6 memory controllers capable of supporting 512 Gbps of bandwidth, the up to 8 GDDR6 controllers in a Speedster7t device can support an aggregate GDDR6 bandwidth of 4 Tbps, delivering the equivalent memory bandwidth of an HBM-based FPGA at a fraction of the cost.

"Micron is pleased to collaborate with Achronix to enable the world's first FPGA with direct attached GDDR6 for high-bandwidth memory requirements," said Mal Humphrey, Vice President of Marketing for Micron's Compute and Networking Business Unit. "Innovative and scalable solutions like these will drive differentiation in areas of AI where heterogeneous compute options, combined with high-performance memory, are needed to accelerate data insights."

Along with this extraordinary memory bandwidth, Speedster7t devices include the industry's highest performance interface ports to support extremely high-bandwidth data streams. Speedster7t devices have up to 72 of the industry's highest performance SerDes that can operate from 1 to 112 Gbps plus hard 400G Ethernet MACs with forward error correction (FEC), supporting 4x 100G and 8x 50G configurations, plus hard PCI Express Gen5 controllers with 8 or 16 lanes per controller.

Super-efficient Data Movement

While the many terabits of data from the Speedster7t high-speed I/O and memory ports would easily overwhelm the routing capacity of a conventional FPGA's bit-oriented programmable-interconnect fabric, the Speedster7t architecture includes an innovative, high-bandwidth, two-dimensional NoC that spans horizontally and vertically over the FPGA fabric, connecting to all of the FPGA's high-speed data and memory interfaces. Acting like a superhighway network superimposed on the city street system of the FPGA interconnect, the Speedster7t NoC supports the high-bandwidth communication needed between on-chip processing engines. Each row or column in the NoC is implemented as two 256-bit, unidirectional industry-standard AXI channels operating at a 2 Ghz, delivering 512 Gbps of data traffic in each direction simultaneously.

The implementation of a dedicated 2D NoC greatly simplifies high-speed data movement and ensures that data streams can easily be directed to any of the custom-defined processing engines throughout the FPGA fabric. Most importantly, the NoC eliminates the congestion and performance bottlenecks that occur in traditional FPGAs that use the programmable routing and logic lookup table (LUT) resources to move data streams throughout the FPGA. This high-performance network not only increases the overall bandwidth capacity of Speedster7t FPGAs, but also increases the effective LUT capacity while reducing power.

Security Features for Safety Critical and Hardware Assurance Applications

Speedster7t FPGAs confront the threat of third-party attacks with the most advanced bitstream security features with multiple layers of defense for protecting bitstream secrecy and integrity. Keys are encrypted based on a tamper-resistant physically unclonable function (PUF), and bitstreams are encrypted and authenticated by 256-bit AES-GCM. To defend against side-channel attacks, bitstreams are segmented, with separately derived keys used for each segment, and the decryption hardware employs differential power analysis (DPA) counter measures. Additionally, a 2048-bit RSA public key authentication protocol is used to activate the decryption and authentication hardware. Users can be confident that when they load their secure bitstream, it is the intended configuration because it has been authenticated by RSA public key, AES-GCM private key, and a CRC checksum.

Proven Conversion Path to Low-cost ASIC for High-volume Requirements

Achronix is the only company that offers both standalone FPGAs and Speedcore™ embedded FPGA IP. Speedcore eFPGA IP is the same technology that Achronix uses in its Speedster7t FPGAs, which allows for a seamless conversion from Speedster7t FPGA to ASIC. FPGA applications typically have functions that must remain programmable, while others are fixed functions that are dedicated to the specific system application. For ASIC conversions, the fixed functions can be hardened into the ASIC structure, which reduces die size, cost and power. Customers can expect to get up to 50 percent power reduction and 90 percent cost reduction when they use Speedcore eFPGA IP to convert Speedster7t FPGAs to ASIC.

Availability

The Speedster7t FPGA devices range from 363K to 2.6M 6-input LUTs. The ACE design tools that support all of Achronix's products including Speedcore eFPGA and Speedchip™ FPGA chiplets are available today.

The first devices and development boards for evaluation will be available in Q4 2019.