Addresses reliability challenges across the product lifecycle for automotive, medical, industrial, aerospace and defense applications

MUNICH — (BUSINESS WIRE) — May 8, 2018 — Cadence Design Systems, Inc. (NASDAQ: CDNS) today introduced the Cadence® Legato™ Reliability Solution, the industry’s first software product that meets the challenges of designing high-reliability analog and mixed-signal integrated circuits (ICs) for automotive, medical, industrial, and aerospace and defense applications. The Legato Reliability Solution provides analog designers with the tools they need to manage their design’s reliability throughout the product lifecycle, from initial test through active life through aging.

This press release features multimedia. View the full release here: https://www.businesswire.com/news/home/20180508005696/en/

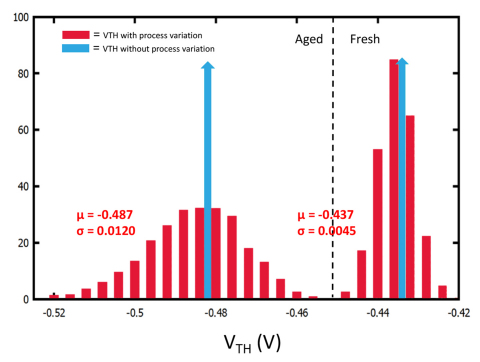

The new aging model in the Cadence® Legato™ Reliability Solution accurately predicts wear-out by analyzing aging acceleration due to temperature and process variation. (Graphic: Business Wire)

Based on the golden, trusted Cadence Spectre® Accelerated Parallel Simulator and the Cadence Virtuoso® custom IC design platform, the Legato Reliability Solution integrates capabilities into an intuitive cockpit to address the reliability concerns of the three phases of the product lifecycle:

- Analog defect analysis accelerates analog defect simulation by up to 100X, reducing test cost and eliminating test escapes, the main source of early failure in IC designs

- Electro-thermal analysis avoids premature failures due to thermal overstress during the product’s useful life

- Advanced aging analysis enables accurate prediction of product wear-out by analyzing aging acceleration due to temperature and process variation.

For more information on the Legato Reliability Solution, visit www.cadence.com/go/legatoreliability.

“Since electronics are the key elements in many mission-critical applications, designing the chips to meet requirements across the entire product lifecycle has become a huge challenge,” said Tom Beckley, Cadence senior vice president and general manager, custom IC and PCB Group. “Designers are faced with the challenge of designing across the entire lifecycle, including eliminating the test escapes that become field failures early in the life cycle, preventing thermal overstress from operating in extreme conditions like under the hood of a car, and designing for 15 years or more of operating lifetime. Our new Legato Reliability solution enables designers to answer these critical questions much earlier in the design process.”

Analog Defect Analysis Reduces Test Cost and Reduces Test Escapes

In this release, Cadence introduces a simulation engine to enable a new test methodology for analog ICs—defect-oriented testing—that expands the capabilities of test far beyond what is traditionally achieved by just performing functional and parametric tests. Defect-oriented testing allows designers to evaluate the ability to eliminate die with manufacturing defects and resulting test escapes that cause field failures. It can also be used to optimize wafer test, reducing the number of tests required to achieve the target defect coverage by eliminating over-testing and potentially reducing the number of tests up to 30 percent. Customer experience with the tool indicates that it accelerates defect simulation by more than 100X.

“Analog defect simulation is becoming very important for us to meet our customers’ expectations,” stated Dieter Härle, project manager, Infineon Austria. “We tested the Legato Reliability Solution and were able to accelerate the simulation time by a factor of more than 100. We verified the solution and plan to adopt it for use in our production flow.”

Electro-Thermal Analysis Prevents Thermal Overstress

In this release, Cadence is introducing a dynamic electro-thermal simulation engine. For automotive designers, for example, actual usage results in significant temperature rise during normal operation due to on-chip losses and power dissipated in the switches. In addition, these components need to operate in hostile environments under the hood of an automobile. The combination of high-power dissipation in a high-temperature environment can result in thermal overstress that can result in failure during normal operation. Dynamic electro-thermal simulation allows designers to simulate the on-chip temperature rise and validate the operation of over temperature protection circuits.

Advanced Aging Analysis Predicts Product Wear-out

Cadence is the recognized leader in aging analysis, providing technologies like RelXpert and AgeMOS to analyze the device degradation due to electrical stress. In this release, Cadence is enhancing aging analysis to include the effects that accelerate device wear-out including temperature and process variation. Cadence also provides a new aging model for device degradation in advanced nodes with FinFET transistors. This holistic approach to aging analysis allows designers to achieve their design lifetime targets with less over-design.

About Cadence

Cadence enables electronic systems and semiconductor companies to create

the innovative end products that are transforming the way people live,

work and play. Cadence software, hardware and semiconductor IP are used

by customers to deliver products to market faster. The company’s System

Design Enablement strategy helps customers develop differentiated

products—from chips to boards to systems—in mobile, consumer, cloud

datacenter, automotive, aerospace, IoT, industrial and other market

segments. Cadence is listed as one of Fortune Magazine’s 100 Best

Companies to Work For. Learn more at

cadence.com .