Built on a new, faster processor architecture, the fifth-generation Vision Q6 DSP targets the smartphone, surveillance camera, automotive, AR/VR, drone and robotics markets

SAN JOSE, Calif. — (BUSINESS WIRE) — April 11, 2018 — Cadence Design Systems, Inc. (NASDAQ: CDNS) today announced the Cadence® Tensilica® Vision Q6 DSP, its latest DSP for embedded vision and AI built on a new, faster processor architecture. The fifth-generation Vision Q6 DSP offers 1.5X greater vision and AI performance than its predecessor, the Vision P6 DSP, and 1.25X better power efficiency at the Vision P6 DSP’s peak performance. The Vision Q6 DSP is targeted for embedded vision and on-device AI applications in the smartphone, surveillance camera, automotive, augmented reality (AR)/virtual reality (VR), drone and robotics markets. For more information, visit www.cadence.com/go/visionq6.

This press release features multimedia. View the full release here: https://www.businesswire.com/news/home/20180411005039/en/

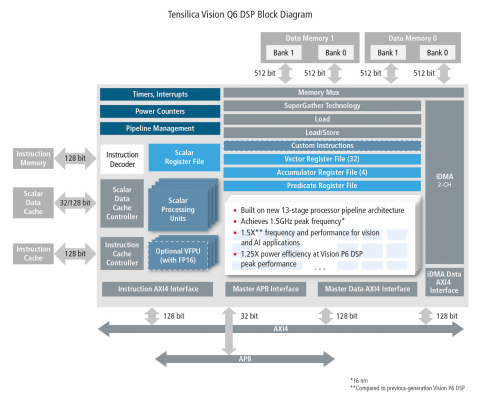

Built on a new, faster processor architecture, the Cadence® Tensilica® Vision Q6 DSP offers 1.5X greater vision and AI performance than its predecessor, the Vision P6 DSP, and 1.25X better power efficiency at the Vision P6 DSP’s peak performance. The Vision Q6 DSP is targeted for embedded vision and on-device AI applications in the smartphone, surveillance camera, automotive, AR/VR, drone and robotics markets. (Graphic: Business Wire)

A deeper, 13-stage processor pipeline and system architecture designed for use with large local memories enable the Vision Q6 DSP to achieve 1.5GHz peak frequency and 1GHz typical frequency at 16nm, in the same floorplan area as the Vision P6 DSP. As a result, designers using the Vision Q6 DSP can develop high-performance products that meet increasing vision and AI demands and power-efficiency needs.

Additional Vision Q6 DSP Features and Benefits

- An enhanced DSP instruction set results in up to 20 percent fewer cycles than the Vision P6 DSP for embedded vision applications/kernels such as Optical Flow, Transpose and warpAffine, and commonly used filters such as Median and Sobel

- 2X system data bandwidth with separate master/slave AXI interfaces for data/instructions and multi-channel DMA alleviates memory bandwidth challenges in vision and AI applications, and also reduces latency and overhead associated with task switching and DMA setup

- Backwards compatibility with the Vision P6 DSP, so customers can preserve their software investment for an easy migration

- Optional vector floating point unit (VFPU) also supports half precision (FP16)

“Cadence has gained traction with its Vision P5 and P6 DSPs, which have been designed into multiple generations of mobile application processors from leading providers,” said Mike Demler, senior analyst at The Linley Group. “SoC providers are seeing an increased demand for vision and AI processing to enable innovative user experiences like real-time effects at video capture frame rates. The Q6 offers a significant performance boost relative to the P6, but it retains the programmability developers need to support rapidly evolving neural network architectures. This is a compelling value proposition for SoC providers who also want the flexibility to do both vision and AI processing.”

The Vision Q6 DSP supports AI applications developed in the Caffe, TensorFlow and TensorFlowLite frameworks through the Tensilica Xtensa® Neural Network Compiler (XNNC). The XNNC maps neural networks into executable and highly optimized high-performance code for the Vision Q6 DSP, leveraging a comprehensive set of optimized neural network library functions. The Vision Q6 DSP also supports the Android Neural Network (ANN) API for on-device AI acceleration in Android-powered devices. The software environment also features complete and optimized support for more than 1,500 OpenCV-based vision and OpenVX library functions, enabling fast, high-level migration of existing vision applications.

“We have been working closely with Cadence to develop AI and vision-based applications. Features such as wide-vector SIMD processing, VLIW instructions, a large number of 8-bit and 16-bit MACs, and scatter/gather intrinsics make Vision DSPs ideal platforms for demanding neural network and vision algorithms,” said Frison Xu, marketing VP at ArcSoft. “Cadence Vision DSPs are being adopted in a large number of end-user applications such as mobile, automotive, surveillance cameras and AR/VR, allowing easy access to platforms to deploy our software.”

“As a valued partner, Cadence provides access to a high-performance, low-power computing environment for our advanced 3D capture and SLAM technology,” said Ken Lee, CEO of VanGogh Imaging. “The Tensilica Vision DSP’s performance characteristics, combined with its highly tuned vision libraries and a robust development environment, enabled a power-efficient implementation of our algorithms and shortened our development cycle.”

The Vision Q6 DSP builds upon the highly successful Vision P6 DSP, which

has been designed into leading mobile application processors including

the Kirin 970 from HiSilicon. Both the Vision P6 DSP and the Vision Q6

DSP are designed for general-purpose embedded vision and on-device AI

applications requiring performance ranging from 200 to 400 GMAC/sec.

With its 384 GMAC/sec peak performance, the Vision Q6 DSP is well suited

for high-performance systems and applications. The Vision Q6 DSP can be

paired with the Vision C5 DSP for applications requiring greater than

384 GMAC/sec AI performance.