TOKYO — (BUSINESS WIRE) — January 31, 2014 — Toshiba Corporation (TOKYO:6502) today announced the launch of photorelays in the industry’s smallest[1] package. Shipment of mass production products starts from today.

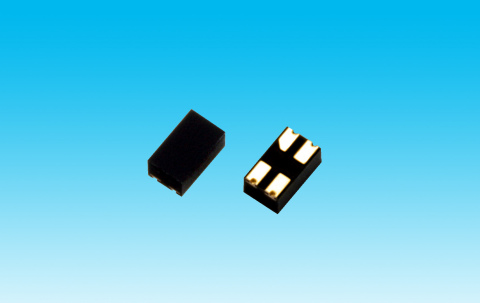

Toshiba: VSON (Very Small Outline Non-leaded) Package Photorelays (Photo: Business Wire)

The new products, “TLP3403” and “TLP3412”, utilize the industry’s smallest package for photocouplers, the Toshiba-developed VSON (Very Small Outline Non-leaded) package. Compared to equivalent Toshiba products in a USOP package, the new photorelays reduce the assembly area by 50% and volume by 60%. This can contribute to the development of smaller and thinner sets and also makes it possible to increase the number of photorelays on a circuit board to 1.3 times to 1.5 times that of conventional products.

Also, by using a new internal structure, a chip-on-chip structure[2], the new products, while retaining the same electrical characteristics as conventional USOP package products, secure improved high-frequency characteristics, which are necessary for signal transmission. The new photocouplers are suitable for various tester applications, especially for use in power-line switching and measuring-line switching.

|

Key Specifications of New Products |

||||

| Part Number | TLP3403 | TLP3412 | ||

| Package Dimension |

Area: 1.5 mm × 2.5 mm (max)

Height: 1.3 mm (max) |

|||

| On-state Current | 1 A (max) | 0.4 A (max) | ||

| On-state Resistance | 0.18 Ω (typ), 0.22 Ω (max) | 1 Ω (typ), 1.5 Ω (max) | ||

| Off-state Voltage | 20 V (min) | 60 V (min) | ||

|

Off-state Capacitance

(Photo side) |

40 pF (typ) | 20 pF (typ) | ||

| Trigger LED Current | 3 mA (max) | |||

|

Equivalent Rise Time

(Pass Characteristic) |

40 ps (typ) | |||

| Isolation Voltage | 300 Vrms(min) | |||