|

Altera's 1G/10Gb Ethernet PHY MegaCore Function

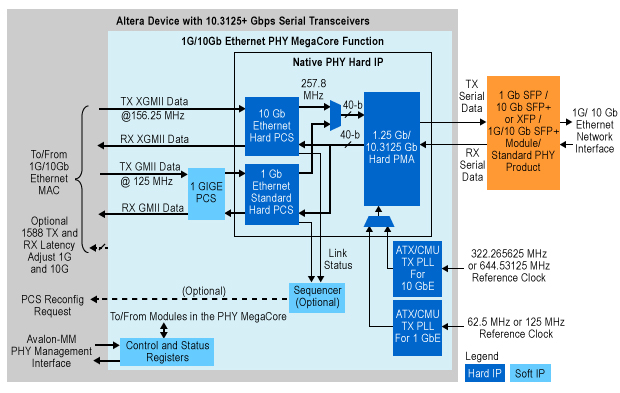

Altera provides a complete 1 Gbps/10 Gbps Ethernet (1G/10GbE) physical coding sublayer (PCS), and physical media attachment (PMA) sublayer intellectual property (IP) known as PHY IP. This IP also supports four data rates 10M/100M/1G/10Gb referred to as 10M-10GbE. This IP is compliant to the SGMII specification at 10/100/1000 Mbps data rates, and compliant to the IEEE 802.3 Ethernet 1000BASE-X and 10GBASE-R standards at 1G/10Gbps data rates. Altera's 1G/10GbE PHY enables connectivity at 1 Gbps over 1Gb Ethernet SFP optical or copper modules and PHY devices, and over 10Gb or 1G/10Gb dual speed Ethernet SFP+ optical modules and PHY devices, and over 10/100/1000Mbps interfaces and Copper PHY devices. The 1G/10GbE Ethernet PHY MegaCore® function allows one FPGA port to be used for various interfaces, saving component cost, board space, and power. This interface PHY can be implemented in Altera® Arria® 10, Stratix® V, and Arria V GZ FPGAs with integrated and silicon-proven serial transceivers operating above 10.3125 Gbps.

Altera's 1G/10GbE PHY IP core is composed of the 1Gb and 10Gb Ethernet serial transceiver hard IP, and soft IP including an SGMII/1GE PCS, optional sequencer, control registers, and status registers for PHY management. This IP can be used for single to multiport Ethernet network interface applications for performance scalability. Altera has developed and tested in hardware the combined 1G/10Gb (10M-10Gb) Ethernet Media Access Controller (MAC) and 1G/10GbE (10M-10GbE) PHY design example.

Figure 1. 1G/10GbE (10M-10GbE) MAC and 1G/10GbE (10M-10GbE) PHY Block Diagram

Easy to Use

- Complete 1G/10GbE and 10M-10GbE PHY solution available to start your design quickly

- Register transfer level (RTL) and post-fit functional simulation for Altera supported Verilog HDL and VHDL simulators

- 1G/10GbE and 10M-10GbE MAC and 1G/10GbE and 10M-10GbE PHY verification testbench and design example

- Development board

- Configuration and generation by the Altera MegaWizardTM Plug-In Manager parameter editor

Robust Solution

- Designed to IEEE 802.3 Ethernet 1000BASE-X and 10GBASE-R standards

- Extensively validated in simulation and in hardware

Protocol Solution

Performance

Typical expected performance and resource utilization figures for this IP core are provided in the Altera Transceiver PHY IP Core User Guide (PDF).

Technical Support

For technical support on this IP core, please visit Altera mySupport online issue tracking system. You can also search for related topics on this function in the Knowledge Base.

|