Back-end-of-line compatible architecture paves the way to high-density 3D-DRAM memories

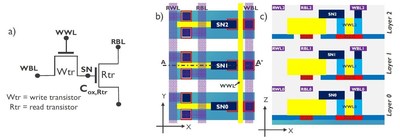

LEUVEN, Belgium, Dec. 15, 2020 — (PRNewswire) — This week, at the 2020 International Electron Devices Meeting, imec, a world-leading research and innovation hub in nanoelectronics and digital technologies, presents a novel dynamic random-access memory (DRAM) cell architecture that implements two indium-gallium-zinc-oxide thin-film transistors (IGZO-TFTs) and no storage capacitor. DRAM cells in this 2T0C (2 transistor 0 capacitor) configuration show a retention time longer than 400s for different cell dimensions – significantly reducing the memory's refresh rate and power consumption. The ability to process IGZO-TFTs in the back-end-of-line (BEOL) reduces the cell's footprint and opens the possibility of stacking individual cells. These breakthrough results pave the way towards low-power and high-density monolithic 3D-DRAM memories.Scaling traditional 1T1C (one transistor one capacitor) DRAM memories beyond 32Gb die density faces two major challenges. First, difficulties in Si-based array transistor scaling make it challenging to maintain the required off-current and world line resistance with decreasing cell size. Second, 3D integration and scalability – the ultimate path towards high-density DRAM – is limited by the need for a storage capacitor. Imec presents a novel DRAM architecture that responds to both challenges, thereby offering a scaling path towards low-power high-density 3D-DRAM memories.

The new architecture implements two IGZO-TFTs – which are well known for their very low off-current – and no storage capacitor. In this 2T0C configuration, the parasitic capacitance of the read transistor serves as the storage element. Resulting DRAM cells exhibit a retention time >400s thanks to an extremely low (extracted) off-current of 3x10-19A/µm. These breakthrough results were obtained for optimized scaled IGZO transistors (with 45nm gate length) processed on 300mm wafers. Optimization was directed towards suppressing the impact of oxygen and hydrogen defects on both on-current and threshold voltage – one of the main challenges for developing IGZO-TFTs.

Gouri Sankar Kar, Program Director at imec: "Besides the long retention time, IGZO-TFT-based DRAM cells present a second major advantage over current DRAM technologies. Unlike Si, IGZO-TFT transistors can be fabricated at relatively low temperatures and are thus compatible with BEOL processing. This allows us to move the periphery of the DRAM memory cell under the memory array, which significantly reduces the footprint of the memory die. In addition, the BEOL processing opens routes towards stacking individual DRAM cells, hence enabling 3D-DRAM architectures. Our breakthrough solution will help tearing down the so-called memory wall, allowing DRAM memories to continue playing a crucial role in demanding applications such as cloud computing and artificial intelligence."

About imec

Imec is a world-leading research and innovation hub in nanoelectronics and digital technologies. The combination of our widely acclaimed leadership in microchip technology and profound software and ICT expertise is what makes us unique. By leveraging our world-class infrastructure and local and global ecosystem of partners across a multitude of industries, we create groundbreaking innovation in application domains such as healthcare, smart cities and mobility, logistics and manufacturing, energy and education.

As a trusted partner for companies, start-ups and universities we bring together more than 4,000 brilliant minds from over 97 nationalities. Imec is headquartered in Leuven, Belgium and has distributed R&D groups at a number of Flemish universities, in the Netherlands, Taiwan, USA, and offices in China, India and Japan. In 2018, imec's revenue (P&L) totaled 583 million euro. Further information on imec can be found at www.imec-int.com.

Imec is a registered trademark for the activities of IMEC International (a legal entity set up under Belgian law as a "stichting van openbaar nut"), imec Belgium (IMEC vzw supported by the Government of Flanders), imec the Netherlands (Stichting IMEC Nederland, part of Holst Centre which is supported by the Dutch Government), imec Taiwan (IMEC Taiwan Co.), imec China (IMEC Microelectronics (Shanghai) Co. Ltd.), imec India (Imec India Private Limited) and imec Florida (IMEC USA nanoelectronics design center).

![]() View original content to download multimedia:

http://www.prnewswire.com/news-releases/imec-demonstrates-capacitor-less-igzo-based-dram-cell-with-400s-retention-time-301192610.html

View original content to download multimedia:

http://www.prnewswire.com/news-releases/imec-demonstrates-capacitor-less-igzo-based-dram-cell-with-400s-retention-time-301192610.html

SOURCE Imec

| Contact: |

| Company Name: Imec, International Electron Devices Meeting

Jade Liu, Press Officer, T +32 16 28 16 93, M +32 495 71 74 52 Email Contact Web: http://www.imec-int.com |