TOKYO — (BUSINESS WIRE) — April 27, 2015 — Toshiba Corporation’s (TOKYO:6502) Semiconductor & Storage Products Company today announced the launch of a low-input current drive transistor output photocoupler in a low-height SO6L package, which can be used to replace conventional DIP4 pin package products. The new product, "TLP383", starts shipments from today.

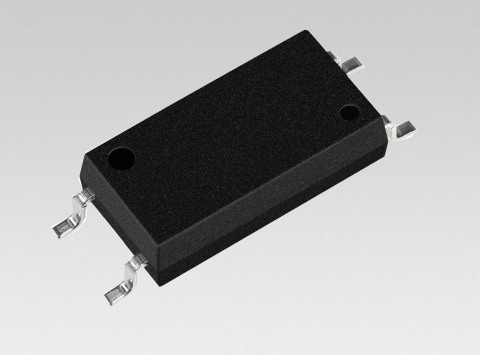

Toshiba: Low-height Package Low-input Current Drive Transistor Output Photocoupler "TLP383" (Photo: Business Wire)

The new product incorporate Toshiba's original high output infrared LEDs and guarantee the same CTR (Current Transfer Ratio) at 0.5mA input current and at 5.0mA input current.

The new photocoupler has a low height of 2.3mm (max), an approximately 45% reduction from Toshiba conventional DIP4 package products. At the same time, the new product has an isolation specification equivalent to DIP4 wide lead type package products and guarantees a creepage and clearance distance of 8mm (min), and isolation voltage of 5000Vrms (min). With its low height, the “TLP383” can be used in situations where there are strict height restrictions, such as on motherboards, and contribute to the development of smaller sets. It can be used for applications including inverter interfaces and general-purpose power supplies.

|

Key Specifications of New Product |

|||||||||

| Part Number | TLP383 | ||||||||

| Current Transfer Ratio (CTR [Note]) | 50 to 600%@IF=0.5mA /5mA, VCE=5V | ||||||||

| Turn-off Time(tOFF) | 30μs (typ) @IF=1.6mA, VCC=5V, RL=4.7kΩ | ||||||||

| Operating Temperature Range(T opr ) | -55 to 125˚C | ||||||||

| Isolation Voltage(BV s ) | 5000 Vrms | ||||||||

| Safety Standard | UL, cUL, VDE, CQC | ||||||||

|

[Note] Corresponds to each CTR rank, such as GR and GB. Please check the datasheet for details. |

|||||||||